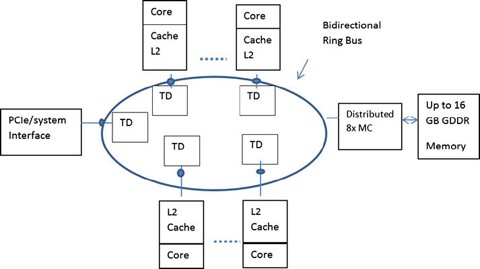

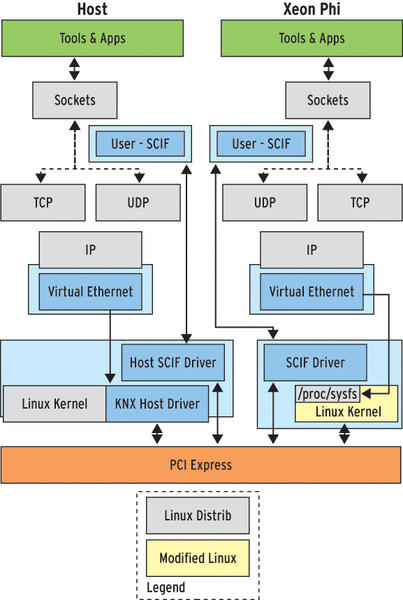

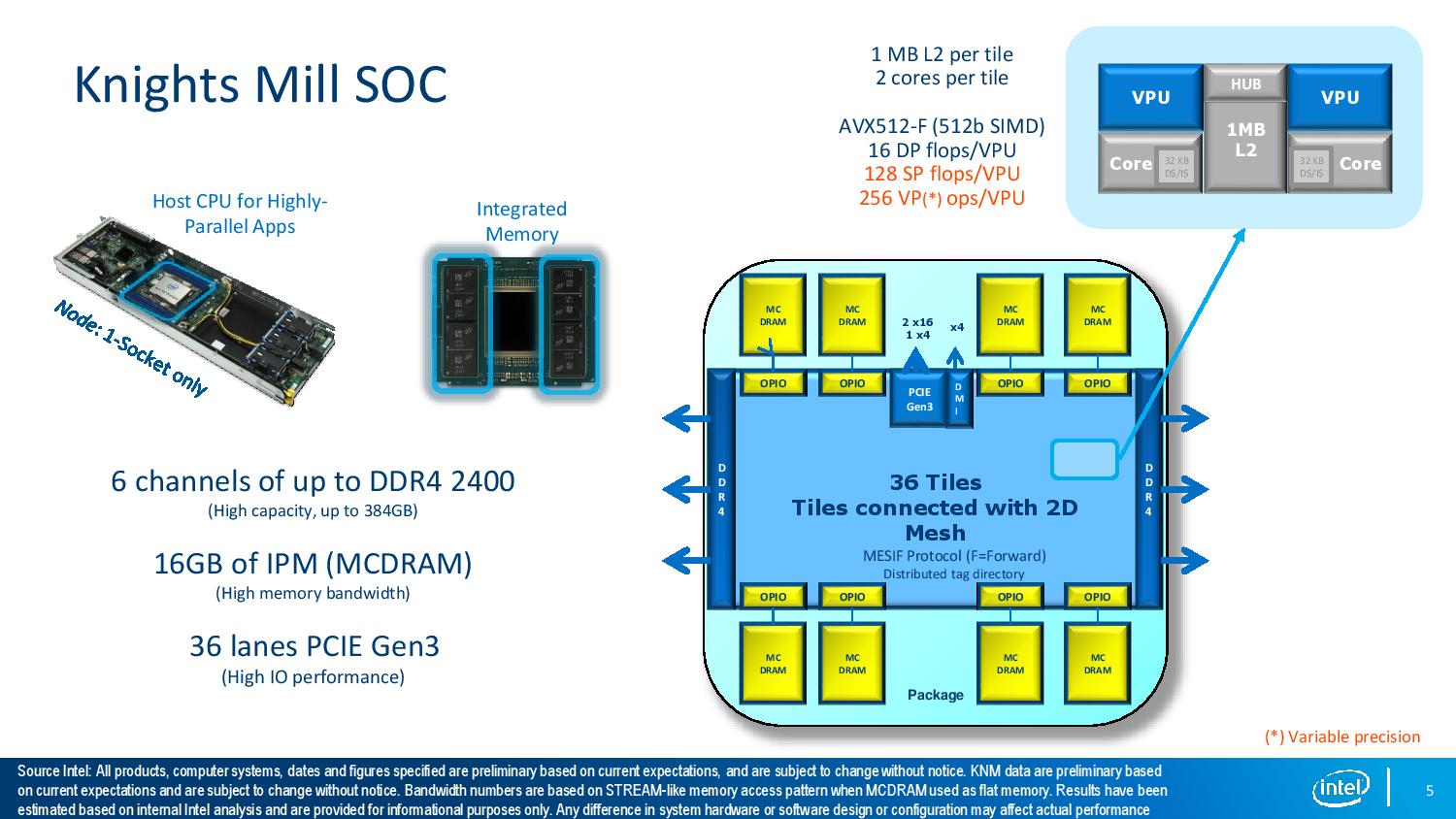

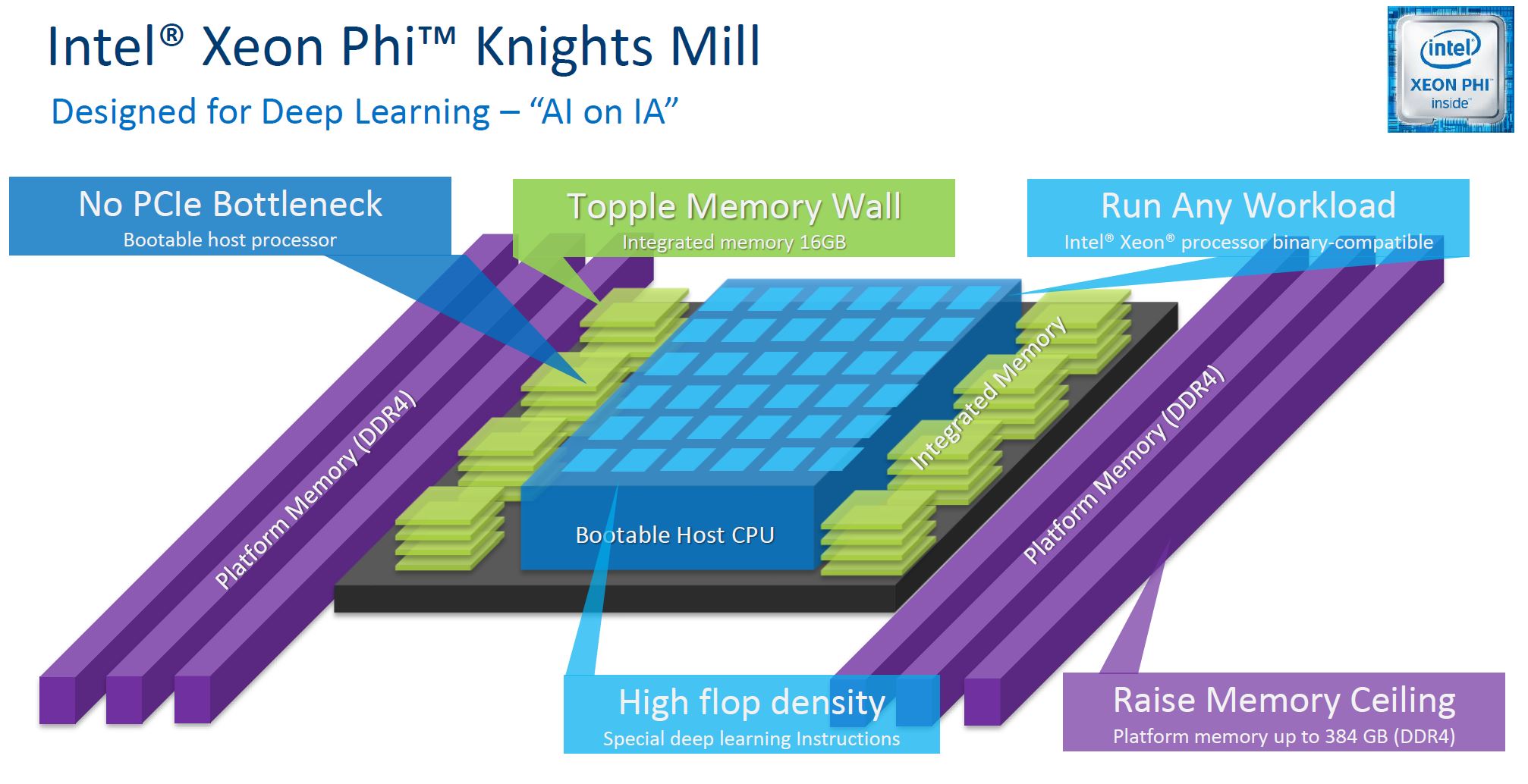

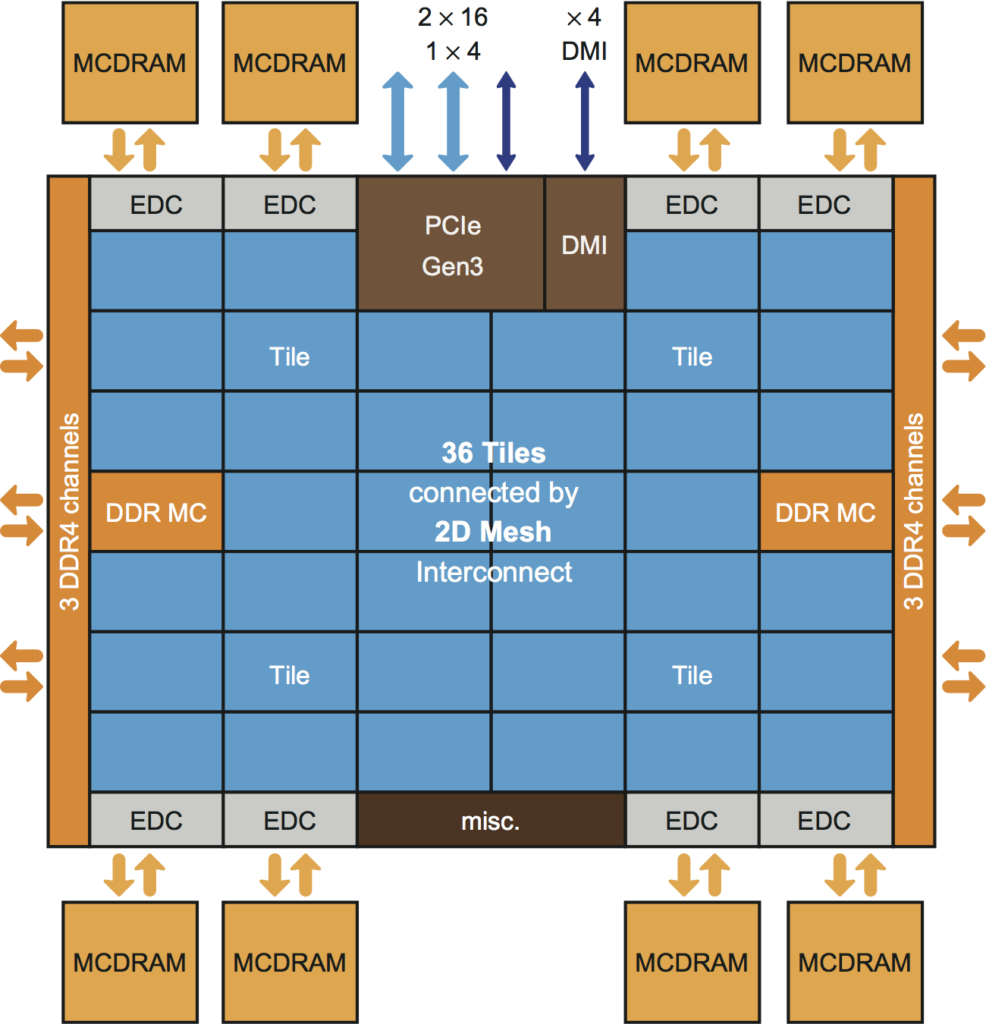

Schematic of Xeon Phi Knights Landing CPU showing the MIC architecture... | Download Scientific Diagram

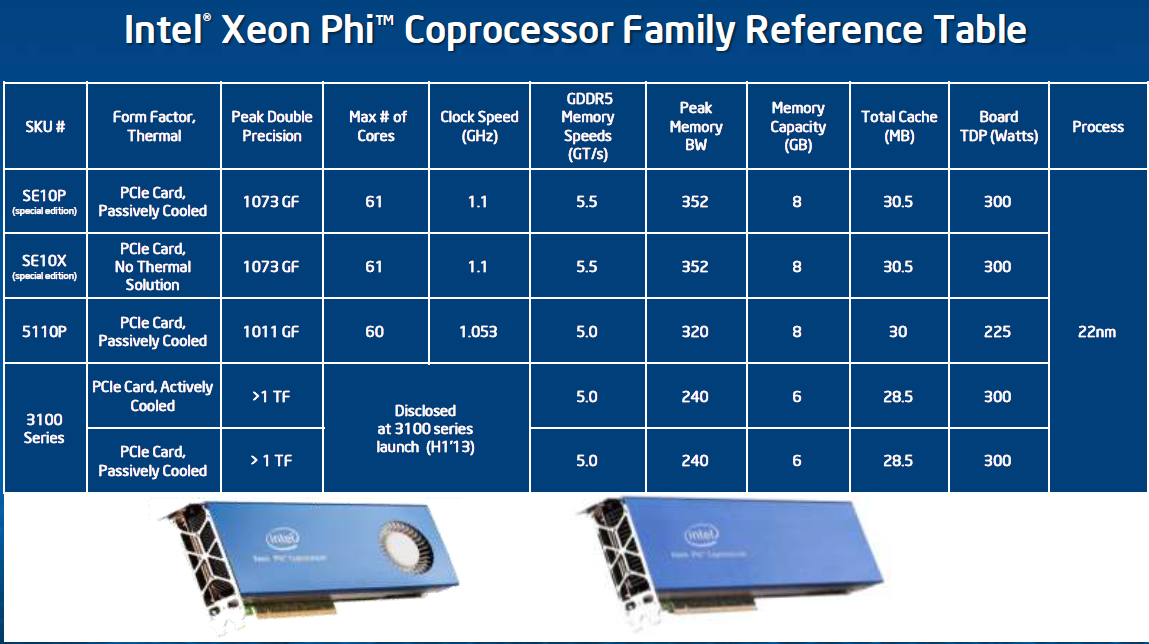

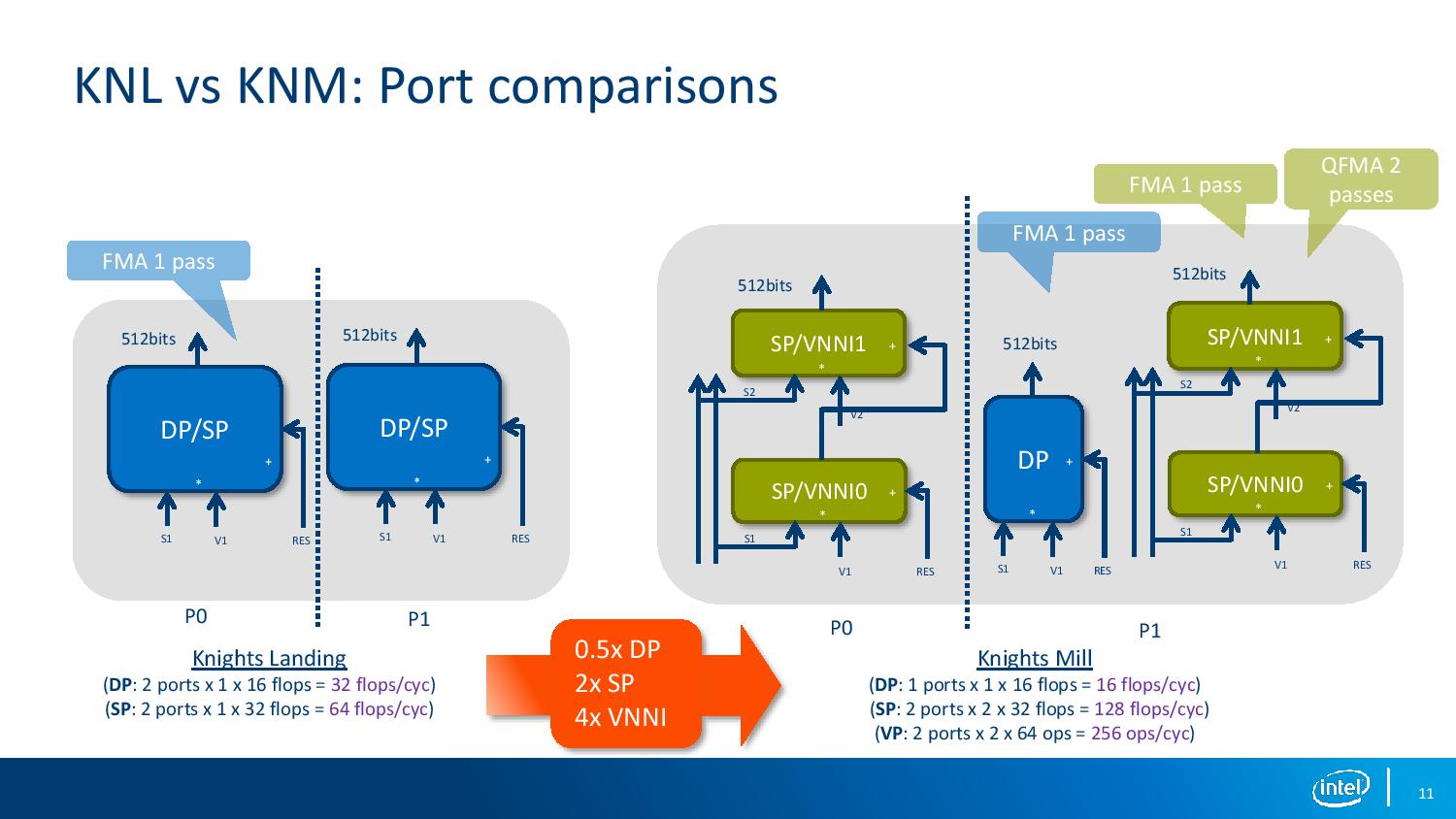

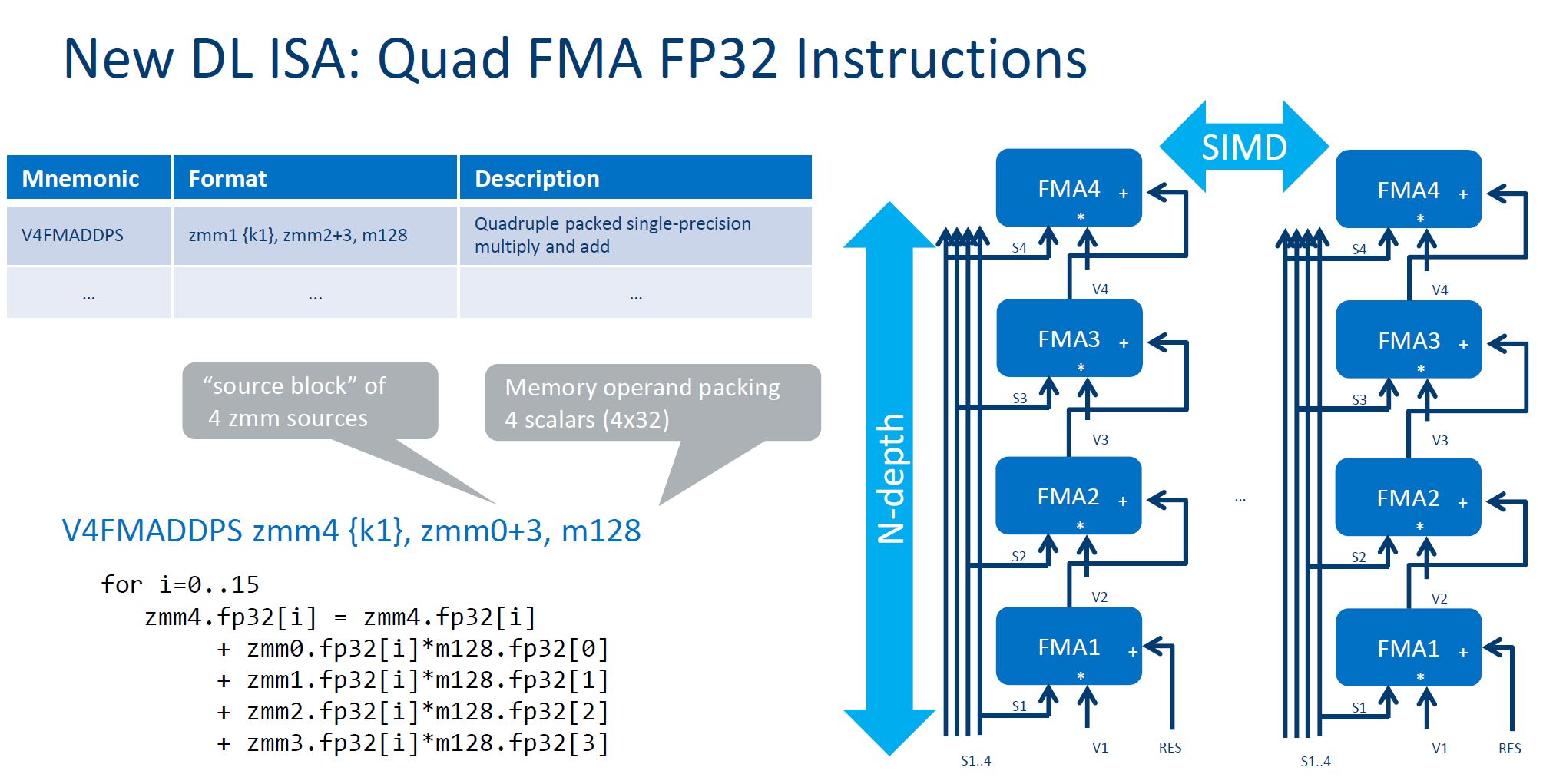

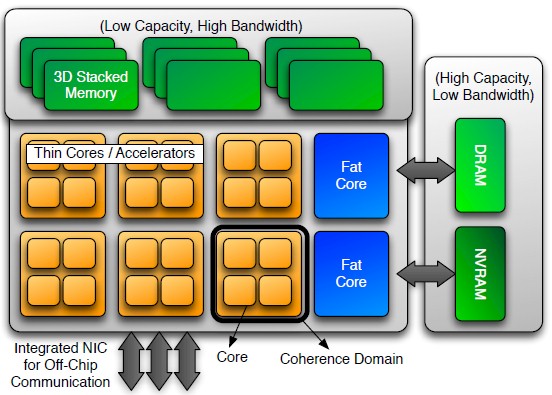

For Intel, the Future of Supercomputing is Phi | Data Center Knowledge | News and analysis for the data center industry

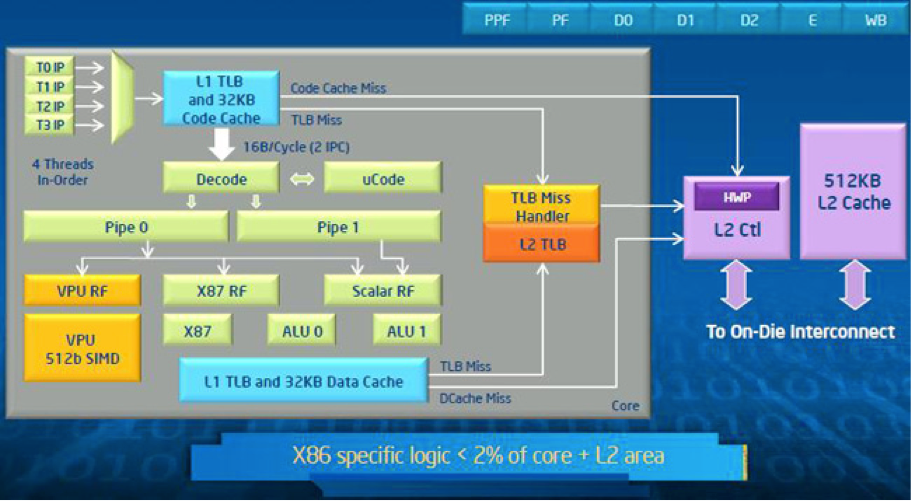

Intel Xeon Phi Processor Programming in a Nutshell - High-Performance Computing News Analysis | insideHPC

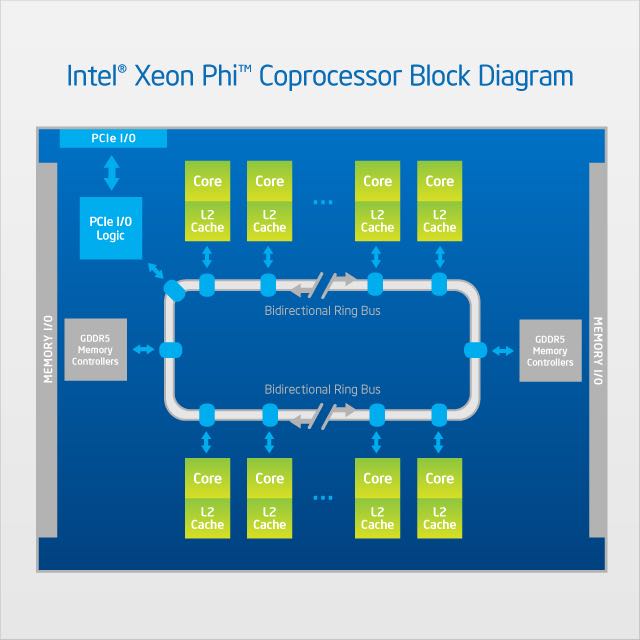

Intel Xeon Phi Coprocessor Architecture and Tools: The Guide for Application Developers | SpringerLink